W ciągu najbliższych kilku lat może zakończyć się produkcja takich procesorów, jakie dziś znamy. Przyzwyczailiśmy się, że ich ciągły rozwój prowadzi do powstawania coraz lepszych desktopów, notebooków, tabletów i smartfonów, jednak na przeszkodzie stają mu nieubłagane prawa fizyki. Mimo to na razie punktem odniesienia dla branży IT wciąż pozostaje prawo Moore’a. Pół wieku temu współzałożyciel Intela prognozował, że liczba tranzystorów w mikroprocesorze będzie podwajała się co 24 miesiące. Największy z producentów daje jeszcze radę realizować to założenie, co dwa lata zmniejszając tranzystory. Przykładowo współczesny procesor Haswell składa się z ok. 1,4 mld tranzystorów, podczas gdy 10 lat temu w układzie Pentium 4 mieściło się ich zaledwie 100 milionów. Konkurenci Intela – Samsung, TSMC czy Globalfoundries – na tyle, na ile potrafią, starają się dotrzymywać mu kroku.

Im więcej tranzystorów mieści się w układzie o ograniczonej objętości, tym więcej ciepła one emitują. Z tego względu pojawia się tzw. ciemny krzem: podczas pracy mikroprocesora nie mogą być jednocześnie wykorzystywane wszystkie jego elementy. Jak dowodzą amerykańscy badacze, przy niezmienionej technologii produkcji w 2018 roku nieaktywna może pozostawać nawet połowa tranzystorów tworzących przeciętny procesor – inaczej układ po prostu się spali. Już od dawna w miejscu stoi wyścig, którego celem było uzyskiwanie coraz większych częstotliwości taktowania – również w tym przypadku barierę stanowi temperatura. Zamiast przyspieszać taktowanie, producenci zwiększają zatem liczbę rdzeni i upychają więcej tranzystorów w pamięci podręcznej. W najbliższych latach pojawią się jednak coraz większe przeszkody, które w końcu uniemożliwią dalsze zmniejszanie tranzystorów przy wykorzystaniu dotychczasowej technologii. Dla utrzymania tempa rozwoju mikroprocesorów stanie się więc konieczne wprowadzenie nowych metod – inaczej prawo Moore’a trzeba będzie odesłać do lamusa. W artykule przedstawiamy niektóre pomysły inżynierów.

Nowe pomysły na tranzystory

Wytwórca mikroprocesorów potrafiący wytwarzać najmniejsze tranzystory ma potężną przewagę: może oferować szybsze procesory, bardziej energooszczędne urządzenia mobilne i pojemniejsze dyski SSD niż którykolwiek z konkurentów. Tranzystory są właściwymi jednostkami obliczeniowymi oraz jednostkami pamięci każdego komputera, gdyż każdy taki układ może reprezentować jeden bit. Zmniejszając tranzystory, producenci mikroprocesorów dotarli już do rzędu wielkości, który oprócz nich interesuje przede wszystkim mikrobiologów: wirus grypy mierzy od 80 do 120 nanometrów (nm), a tranzystor nowoczesnego CPU – od 60 do 90 nm.

Tranzystory są zbudowane z półprzewodzącego krzemu, w którego strukturę wpleciono atomy innych pierwiastków. Ta domieszka pozwala modyfikować przewodność krzemu: półprzewodnik typu “n” tworzący źródło i dren (patrz: infografika po prawej) zawiera na przykład atomy fosforu, mające więcej elektronów walencyjnych niż atomy krzemu i łatwiej uwalniające je pod wpływem napięcia. Podłoże tworzy natomiast materiał z domieszką typu “p”, na przykład atomów boru, które mogą przyjmować wolne elektrony. Po przyłożeniu napięcia do bramki, w kanale między źródłem a drenem zaczyna płynąć prąd – tranzystor jest włączony. Kiedy zmniejszy się taki układ, a w szczególności długość bramki, może on działać efektywniej, jednak pojawiają się problemy: warstwa zubożona z niedomieszkowanego półprzewodnika, rozdzielająca obszary materiału z domieszką typu “p” i “n” staje się coraz cieńsza i bardziej przepuszczalna, przez co elektrony bez przeszkód przepływają ze źródła i drenu do podłoża. Jednocześnie warstwa ta zajmuje relatywnie coraz większą część kanału, co ułatwia niechciany przepływ elektronów ze źródła do drenu. Te tzw. prądy upływu odpowiadają już za prawie 40 proc. zużycia energii przez procesory.

Nowe typy procesorów

Z tego powodu wszyscy znaczący producenci procesorów zaprzestają stosowania tranzystorów o klasycznej budowie w procesie technologicznym 20 nm. O kłopotach wynikających ze zmniejszania tranzystorów świadczy to, że oznaczenia procesów technologicznych coraz bardziej odbiegają od prawdziwej długości bramki: na papierze tranzystory kurczą się bardziej niż w rzeczywistości (patrz: wykres po prawej). Chcąc budować jeszcze mniejsze tranzystory, trzeba zmodyfikować ich konstrukcję. Tworząc tranzystory Tri-Gate, Intel jako pierwszy wytwórca zastosował w praktyce koncepcję FinFET, a w latach 2014–15 dołączą do niego pozostałe firmy z branży. W tranzystorach FinFET kanał, źródło i dren są odseparowane od podłoża (patrz: infografika po prawej). Materiał podłoża nie jest domieszkowany, zaś kanał jest – najwyżej niewielką ilością obcych atomów. Wskutek tego znacznemu ograniczeniu ulegają prądy upływu i możliwe jest wprowadzanie mniejszych procesów technologicznych – aż do 10 nm.

Również stosując tranzystory FinFET, producenci procesorów nie są do końca szczerzy: podawane przez nich wielkości procesu technologicznego odnoszą się do efektywności typowych tranzystorów. Tranzystory Tri-Gate o długości bramki 30 nm dorównują pod względem zużycia energii i wydajności klasycznym tranzystorom w rozmiarze 22 nm – i taką wielkością jest oznaczany ich proces technologiczny. Analityk rynku mikroprocesorów Malcolm Penn prognozuje, że rzeczywista długość bramki tranzystora w zapowiadanych na przyszły rok procesorach wykonanych w procesie technologicznym 14 nm będzie wynosiła od 17 do 20 nm. Chcąc w latach 2017–18 przekroczyć granicę 10 nm, producenci muszą zastosować inne materiały (patrz: następna strona) i po raz kolejny zmienić konstrukcję tranzystorów: wykorzystanie pełnego potencjału koncepcji FinFET umożliwią nanoprzewody. Elementami funkcjonalnymi tranzystorów zbudowanych z użyciem nanoprzewodów będą wyłącznie źródło, kanał, bramka i dren, przy czym kanał będzie otoczony bramką ze wszystkich stron (patrz: infografika po prawej). Nanoprzewody są jednak na razie jedynie obiektem badań laboratoryjnych, a naukowcom udało się stworzyć wyłącznie kilka prototypów.

Metale zamiast krzemu

Architektura FinFET rozwiązuje wiele problemów wynikających ze zmniejszania tranzystorów. Mogą one być zasilane prądem o niższym napięciu, co przekłada się na mniejsze zużycie energii, a jednocześnie przełączać się z większą szybkością. Redukcja komponentów funkcjonalnych (źródła, drenu i kanału) do wąskiej wystającej “płetwy” powoduje jednak nowe komplikacje, z którymi producenci procesorów będą musieli zmierzyć się najpóźniej przy wprowadzaniu procesu technologicznego 10 nm. Od 2009 roku w konstrukcji komponentów funkcjonalnych tranzystorów wykorzystuje się “rozciągnięty krzem”. Rozciąganie należy rozumieć dosłownie: w strukturę krzemu zostają wprowadzone atomy germanu, przez co dystans między poszczególnymi atomami ulega zwiększeniu. Na warstwę krzemowo-germanową (SiGe) nakłada się warstwę zwykłego krzemu. Obie warstwy łączą się, tworząc regularną strukturę krystaliczną, przy czym wielkość odstępów między atomami zostaje dostosowana do struktury warstwy SiGe. Zwiększenie tych odstępów poprawia przewodność materiału – elektrony przemieszczają się przez przełączony tranzystor nawet o 70 proc. szybciej, niż gdyby był on wykonany ze zwykłego krzemu.

W małych tranzystorach FinFET “płetwa” jest jednak tak cienka, że składa się z zaledwie kilku warstw atomów. Rozciąganie krzemu staje się coraz trudniejsze, a przy procesie technologicznym 10 nm okaże się już niemożliwe. Potencjał krzemu jako głównego materiału półprzewodnikowego zostanie wyczerpany. Odsiecz nadejdzie w postaci nowych materiałów, które przynajmniej częściowo zastąpią krzem. Za idealną podstawę do budowy elementów z domieszką typu “p” uchodzi german, zajmujący w układzie okresowym miejsce bezpośrednio poniżej krzemu i mogący zastąpić go bez większych problemów. Struktura krystaliczna germanu jest naturalnie rozciągnięta, a jego przewodność czterokrotnie przewyższa przewodność krzemu. Elementy tranzystorów wymagające domieszkowania typu “n” mogłyby być wykonane z mieszanki indu, galu i arsenu (InGaAs), mającej sześciokrotnie wyższą przewodność. Już pierwszy prototyp tranzystora z kanałem wykonanym z tego materiału zużywa o połowę mniej energii niż porównywalny tranzystor FinFET z krzemowym kanałem. Analitycy rynkowi prognozują, że nowe materiały zaczną być stosowane na masową skalę od 2017 roku.

Elementy z pojedynczej warstwy atomów

Po 2020 roku, kiedy na horyzoncie ukaże się proces produkcyjny 5 nm, pojawi się zapotrzebowanie na jeszcze mniejsze struktury o wysokiej przewodności elektrycznej. Takie warunki mogą spełnić nanowarstwy 2D, czyli materiały złożone z pojedynczej warstwy atomów (tzw. monowarstwy). Obecnie przedmiotem intensywnych badań jest grafen, czyli siatka atomów węgla. Naukowcy pracują także nad germananem (złożonym z atomów germanu), silicenem (z atomów krzemu) oraz statenem (z atomów cynku). Materiały monowarstwowe nie zastąpią krzemu od razu – początkowo będą tylko jego uzupełnieniem. Najpierw jednak trzeba uporać się ze związanym z nimi problemem: nad ich przewodnością trudno zapanować, a jest to niezbędne, by można było wykorzystać je jako półprzewodniki. Tranzystor z czystego grafenu byłby włączony praktycznie przez cały czas, więc zużywałby mnóstwo prądu.

Materiały monowarstwowe pozwoliłyby za to uniknąć innego kłopotu związanego z miniaturyzacją tranzystorów: obecnie przełączają się one tak prędko, że miedziane obwody nie są w stanie wystarczająco szybko transportować do nich ładunków elektrycznych. Problem jest tym poważniejszy, im mniejszy proces produkcyjny jest wykorzystywany. Naukowcom z japońskiego Narodowego Instytutu Zaawansowanych Nauk Stosowanych i Technologii udało się znaleźć rozwiązanie: miedź zastąpiono grafenem o znacznie wyższej przewodności.

Droga do trzeciego wymiaru

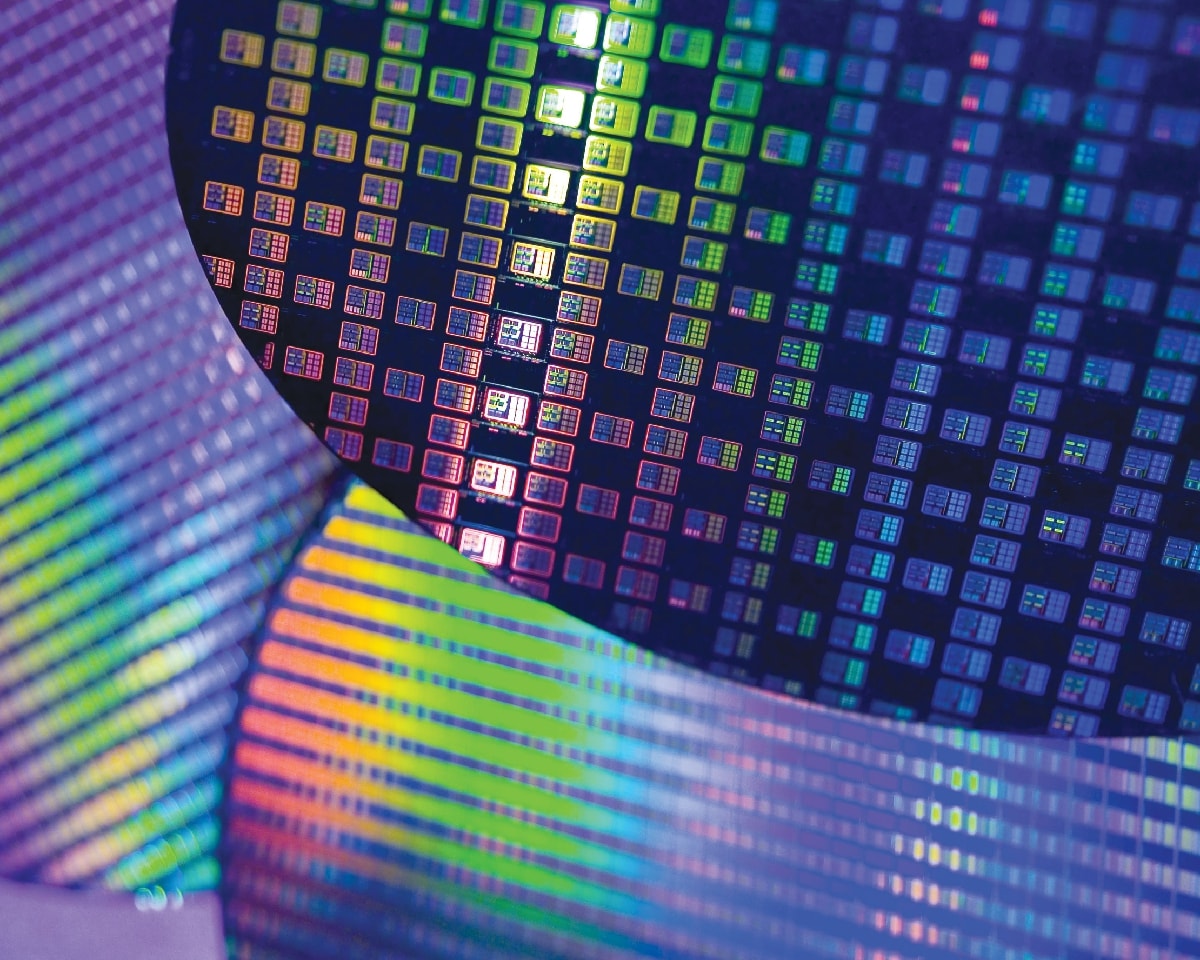

Niemal wszyscy liczący się producenci projektują procesory 3D, w których układy obliczeniowe współpracowałyby z pozostałymi podzespołami bez znaczących opóźnień. Przykładowo na warstwie elementów procesora można umieścić warstwę pamięci RAM, a wyżej – warstwę pamięci flash. Największy niezależny wytwórca układów scalonych – tajwańskie TSMC – ma wprowadzić trójwymiarową integrację elementów zapowiedzianych procesorów 16-nanometrowych. Być może już w 2016 trafią one do topowych smartfonów: prawdopodobnym kandydatem jest iPhone 7, gdyż Apple właśnie rozpoczął współpracę z TSMC. Trójwymiarowa struktura zostanie zbudowana z wykorzystaniem połączeń TSV (Through-Silicon Via): w krzemowych waflach zostaną nawiercone pojedyncze otwory o średnicy do 10 μm, do których zostanie wstrzyknięty materiał przewodzący. W ten sposób przewodnik połączy ułożone warstwowo wafle tworzące procesor 3D

Technologia TSV jest jednak tylko rozwiązaniem przejściowym na drodze do monolitycznych procesorów 3D – w tym przypadku cały układ będzie złożony z pojedynczego bloku materiału, w którym warstwy krzemu zawierające tranzystory będą ze sobą bezpośrednio połączone obwodami o grubości około 100 nm. Jedynie do produkcji najniższej warstwy zostanie wykorzystany typowy wafel krzemowy. Kolejne warstwy, zawierające tranzystory i ścieżki przewodzące, będą nadrukowywane bezpośrednio na niej. By było to możliwe, cały proces produkcyjny musiprzebiegać w temperaturze poniżej 400°C. Ponieważ warstwy będą ułożone bliżej siebie, a obwody elektryczne zostaną jeszcze bardziej zminiaturyzowane, takie rozwiązanie pozwoli zwiększyć szybkość transmisji danych i obniżyć zużycie energii w porównaniu z technologią TSV.

Struktury 3D w dyskach SSD i HDD

Komórki pamięci flash stosowane w dyskach SSD przypominają tranzystory logiczne – różnią się od nich głównie obecnością tzw. bramki swobodnej. Znajduje się ona pomiędzy kanałem a bramką i służy jako swego rodzaju magazyn elektronów. Komórki pamięci obecnie produkowanych dysków SSD mają szerokość poniżej 20 nm, przez co narażone są na podobne problemy związane z miniaturyzacją, jak tranzystory mikroprocesorów. Mała odległość między komórkami sprawia, że zapisane w nich ładunki powodują odchylenia ich stanów. Dalsze zmniejszanie komórek pamięci flash (tak że odległości między nimi skurczą się do 10 nm), spowoduje, że kontroler nie będzie w stanie prawidłowo odczytywać zapisanych w nich wartości. Z tego względu producenci pamięci – Samsung, Toshiba/SanDisk czy Hynix – rezygnują z miniaturyzacji i zamiast tego modyfikują architekturę. Komórki mają być układane warstwowo, tworząc kolumny, z których będzie składał się nośnik. Konstrukcja komórek zostanie uproszczona, tak jak w pamięci V-NAND zaprojektowanej przez Samsunga (patrz: po prawej stronie), a dodatkowo ich żywotność wydłuży się z zaledwie 3000 aż do 35 000 cykli zapisu/odczytu. Koreańczycy planują, że do 2017 uda im się zwiększyć gęstość danych pamięci V-NAND stosowanej w dyskach SSD prawie dziesięciokrotnie – dzisiejsze układy o pojemności 128 Gb urosną do 1 Tb.

Architektury 3D sprawdzą się również w przypadku dysków magnetycznych, których gęstość danych przy zachowaniu klasycznej konstrukcji również osiągnęła maksimum. Liczby spolaryzowanych magnetycznie cząstek reprezentujących pojedynczy bit nie da się już zmniejszyć, gdyż sygnał byłby zbyt słaby, aby głowica mogła go odczytać. Jednym z proponowanych rozwiązań jest zastosowanie nowych stopów metali. Inne postulowali badacze z Międzynarodowego Uniwersytetu Kalifornijskiego: zbudowali oni prototyp dysku, w którym magnesowaniu ulegały trzy nałożone na siebie warstwy materiału. Każda z nich jest odizolowana od pozostałych i ma inne właściwości magnetyczne. Dzięki temu, aby zmienić polaryzację fragmentu każdej warstwy, głowica dysku musi wytworzyć pole magnetyczne o innym natężeniu. Głowica odczytu mierzy łączne natężenie pola magnetycznego wszystkich trzech warstw odpowiadające jednej z ośmiu wartości.